#### QSFP-DD MSA

#### QSFP-DD Specification

for

#### QSFP DOUBLE DENSITY 8X PLUGGABLE TRANSCEIVER

Rev 2.0 March 13, 2017

Abstract: This specification defines: the electrical and optical connectors, electrical signals and power supplies, mechanical and thermal requirements, and the management interface of the pluggable QSFP Double Density (QSFP-DD) module, connector and cage system. This document provides a common specification for systems manufacturers, system integrators, and suppliers of modules.

#### POINTS OF CONTACT:

Tom Palkert Mark Nowell Scott Sommers Co-Chair Technical Editor Co-Chair Molex Cisco Molex 2222 Wellington Court 170 West Tasman Dr 2222 Wellington Court Lisle, IL 60532-1682 Lisle, IL 60532-1682 San Jose, CA 95134 Ph: 952-200-8542 Ph: 613-254-3391 Ph: 630-527-4317 tom.palkert at molex.com mnowell at cisco.com scott.sommers at molex.com

www.qsfp-dd.com

Limitation on use of Information:

This specification is provided "AS IS" with NO WARRANTIES whatsoever and therefore the provision of this specification does not include any warranty of merchantability, noninfringement, fitness for a particular purpose, or any other warranty otherwise arising out of any proposal, specification or sample. The authors further disclaim all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

#### Permissions:

You are authorized to download, reproduce and distribute this document. All other rights are reserved. The provision of this document should not be construed as the granting of any right to practice, make, use or otherwise develop products that are based on the document. Any and all IP rights related to this document and the designs disclosed within, except for the rights expressly mentioned above, are reserved by the respective owners of those IP rights. The following are Promoter member companies of the QSFP-DD MSA.

Broadcom LTD Brocade Cisco Corning Finisar Foxconn Interconnect Technology Huawei LTD Intel Juniper Networks Lumentum Luxtera Mellanox Molex LLC Oclaro, Inc. TE Connectivity

The following are contributing member companies of the QSFP-DD MSA.

Amphenol Applied Optoelectronics Apresia Celestica Ciena ColorChip DellEMC Delta Fujitsu Genesis H3C Innovium Inphi Ixia Kaiam Leoni Lorom Cable Connection LuxshareICT Macom MaxLinear MultiLane Neophotonics Nokia Panduit PHY-SI Ranovus Samtec Semtech Senko Sicoya The Siemon Company Skorpios Source Photonics Spirent Sumitomo Electric Xilinx Yamaichi 2

Change History:

| Revision | Date          | Changes               |  |  |

|----------|---------------|-----------------------|--|--|

| 1.0      | Sept 19 2016  | First public release  |  |  |

| 2.0      | March 13 2017 | Second public release |  |  |

#### Foreword

The development work on this specification was done by the QSFP-DD MSA, an industry group. The membership of the committee since its formation in Feb 2016 has included a mix of companies which are leaders across the industry.

### TABLE OF CONTENTS

| 1.  | Sc   | cope                                                                          | 7 |

|-----|------|-------------------------------------------------------------------------------|---|

| 1   | .1   | Description of Sections                                                       | 7 |

| 2.  | Re   | ferences                                                                      | 7 |

| 2   | .1   | Industry Documents                                                            | 7 |

| 2   | .2   | Sources                                                                       | 7 |

| 3   | Intr | roduction                                                                     | 8 |

| 3   | .1   | Objectives                                                                    | 8 |

| 3   | .2   | Applications                                                                  | 9 |

| 4 E | lect | rical Specification                                                           | 9 |

| 4   |      | lectrical Connector                                                           | - |

|     |      | .1 Low Speed Electrical Hardware Signals1                                     |   |

|     |      | .2 Low Speed Electrical Specification                                         |   |

|     |      | .3 High Speed Electrical Specification1                                       |   |

| 4   |      | ower Requirements                                                             |   |

|     |      | .1 Power Classes and Maximum Power Consumption                                |   |

|     |      | .2 Host Board Power Supply Filtering2<br>.3 Module Power Supply Specification |   |

|     |      | .4 Host Board Power Supply Noise Output2                                      |   |

|     |      | .5 Module Power Supply Noise Output                                           |   |

|     |      | .6 Module Power Supply Noise Tolerance                                        |   |

| 4   | .3 E | SD2                                                                           | 4 |

| 5 M | echa | nical and Board Definition 2                                                  | 5 |

| 5   | .1 I | ntroduction2                                                                  | 5 |

| 5   | .2 D | atums, Dimensions and Component Alignment2                                    | 6 |

| 5   | .3 M | odule Mechanical Dimensions2                                                  | 8 |

| 5   | .4 M | odule Flatness and Roughness3                                                 | 3 |

| 5   | .5   | Module paddle card dimensions3                                                | 4 |

| 5.6 Module Extraction and Retention Forces                                                                                                                                                                          |                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 5.7 2x1 Electrical Connector Mechanical<br>5.7.1 2x1 Connector and Cage host PCB layout                                                                                                                             |                |

| 5.8 Surface Mount Electrical Connector Mechanical<br>5.8.1 Surface mount connector and cage host PCB layout                                                                                                         |                |

| 5.9 Module Color Coding and Labeling                                                                                                                                                                                | 54             |

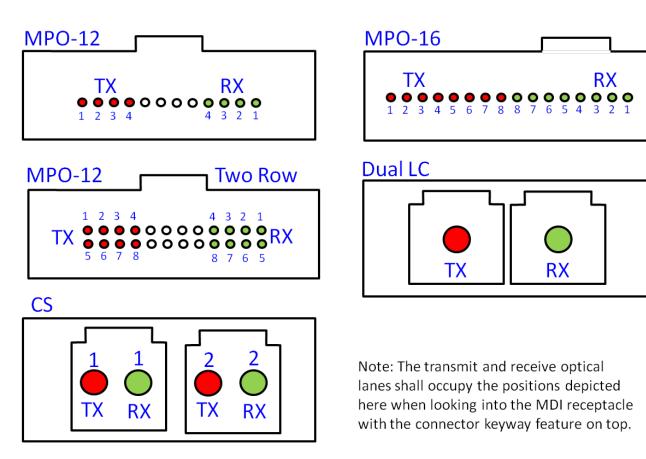

| 5.10 Optical Interface<br>5.10.1 MPO Optical Cable connections<br>5.10.2 Dual LC Optical Cable connection<br>5.10.3 Dual CS Optical Cable connection<br>5.10.4 Electrical data input/output to optical port mapping | 56<br>58<br>58 |

|                                                                                                                                                                                                                     |                |

| 6 Environmental and Thermal                                                                                                                                                                                         |                |

| 6.1 Thermal Requirements                                                                                                                                                                                            | 59             |

| 7 Management Interface                                                                                                                                                                                              | 60             |

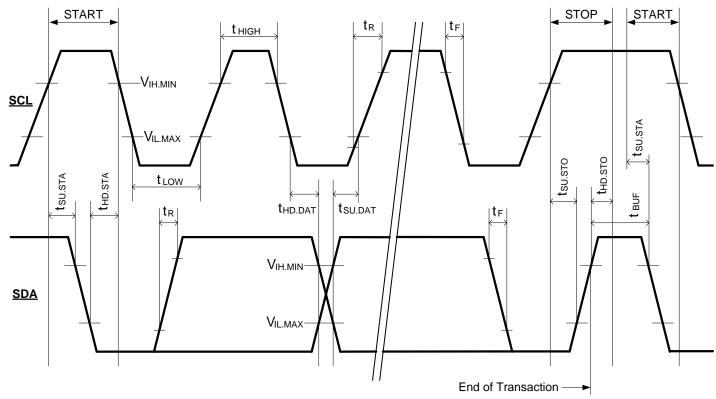

| 7.1 Timing Specification<br>7.1.1 Introduction<br>7.1.2 Management Interface Timing Specification<br>7.1.3 Serial Interface Protocol                                                                                | 60<br>60       |

| 7.2 Memory Interaction Specifications<br>7.2.1 Timing for Soft Control and Status Functions                                                                                                                         |                |

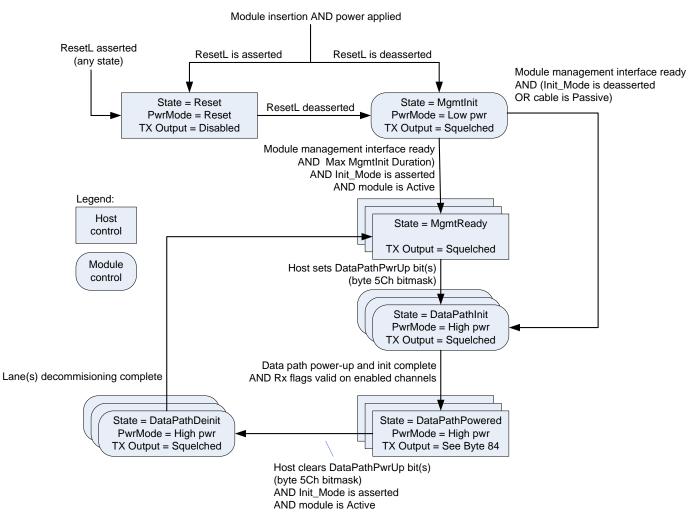

| 7.3 QSFP-DD Initialization State Machine                                                                                                                                                                            |                |

| <pre>7.4 QSFP-DD Memory Map<br/>7.4.1 Lower Page 00h<br/>7.4.2 Upper Page 00h<br/>7.4.3 Upper Page 01h<br/>7.4.4 Upper Page 02h<br/>7.4.5 Upper Page 03h</pre>                                                      |                |

|                                                                                                                                                                                                                     |                |

| Table 1- Pad Function Definition                                                                                                         |       |

|------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 2- Low Speed Control and Sense Signals                                                                                             |       |

| Table 3- Power Classification                                                                                                            |       |

| Table 4- Power Supply specifications, Instantaneous, sustained and steady state current                                                  |       |

| limits                                                                                                                                   |       |

| Table 5- Datums                                                                                                                          |       |

| Table 6- Module flatness specifications                                                                                                  |       |

| Table 7- Insertion, Extraction and Retention Forces                                                                                      |       |

| Table 8- Electrical data input to Optical Port Mapping                                                                                   |       |

| Table 9- Temperature Range Class of operation                                                                                            |       |

| Table 10- Management Interface timing parameters                                                                                         |       |

| Table 11- QSFP-DD Memory Specification                                                                                                   |       |

| Table 12- Writable Memory Blocks                                                                                                         |       |

| Table 13- Timing for QSFP-DD soft control and status functions                                                                           |       |

| Table 14- I/O Timing for Squelch & Disable                                                                                               |       |

| Table 15- Interrupt Flag Classes.                                                                                                        |       |

| Table 16- Lower Page Overview (Lower Page)                                                                                               |       |

| Table 17- Identifier and Status Summary (Lower Page)                                                                                     |       |

| Table 18- Interrupt Flags (Lower Page, active modules only)                                                                              |       |

| Table 19- State Indicators (Lower Page, active modules only)                                                                             |       |

| Table 20- Channel State register encoding                                                                                                |       |

| Table 21- Module Monitors (Lower Page, active modules only)                                                                              |       |

| Table 22- Channel Monitors (Lower Page, active modules only)                                                                             |       |

| Table 23- Control Fields (Lower Page, active modules only)                                                                               |       |

| Table 24- Tx Input Equalization                                                                                                          |       |

| Table 25- Rx Output Pre-emphasis                                                                                                         |       |

| Table 26- Rx Output Amplitude                                                                                                            |       |

| Table 27- Interrupt Masks (Lower Page, active modules only)<br>Table 28- Upper Page 0 Overview (Page 00h)                                | 83    |

|                                                                                                                                          |       |

| Table 29- Identifiers (Page 00h)                                                                                                         |       |

| Table 30- Specification compliance (Page 00h)                                                                                            |       |

| Table 31- Extended Rate Select compliance (Page 00h)                                                                                     |       |

| Table 32- Link Length (Page 00h)Table 33- Device technology (Page 00h)                                                                   |       |

| Table 34- Technology values                                                                                                              |       |

| Table 34- Technology Values                                                                                                              |       |

| Table 36- Options (Page 00h)                                                                                                             |       |

| Table 30- Options (Page 000)         Table 37- Diagnostic Monitoring Type (Page 00h)                                                     |       |

| Table 38- Enhanced Options (Page 00h)                                                                                                    |       |

| Table 39- Device Properties (Page 00h)                                                                                                   |       |

| Table 40- State Duration Encoding                                                                                                        |       |

| Table 40- State Duration Encouring<br>Table 41- Application Table Header (Page 01h, active modules only)                                 |       |

| Table 41- Application lable header (Page Oll, active modules only)                                                                       |       |

| Table 42 Edgacy Table Entry (Fage Off, active modules only)                                                                              |       |

| Table 43- Excended Table Entry (Page 010, active modules only)         Table 44- Upper Page 3 Overview (Page 03h)                        |       |

| Table 44- opper page 5 overview (page 031)         Table 45- Module Thresholds (Page 03h, active modules only)                           |       |

| Table 45- Module Infestiolds (Page 03h, active modules only)         Table 46- Channel Thresholds (Page 03h, active modules only)        |       |

| Table 40- Channel Thresholds (Page 03h, active modules only)         Table 47- Extended Channel Controls (Page 03h, active modules only) |       |

| Table 48- Hardware/Firmware ID (Page 03h, active modules only)                                                                           |       |

| Table to marawate/Filmwate ib (tage off, active modules only)                                                                            | - U U |

# QSFP-DD Rev 2.0

|        | 1: Application Reference Model                                                |    |

|--------|-------------------------------------------------------------------------------|----|

| Figure | 2: Module pad layout                                                          | 12 |

| Figure | 3: Example QSFP-DD Host Board Schematic For Optical Modules                   | 15 |

| Figure | 4: Example QSFP-DD Host Board Schematic for active copper cables              | 16 |

| Figure | 5: Example QSFP-DD Host Board Schematic for passive copper cables             | 17 |

| Figure | 6: Recommended Host Board Power Supply Filtering                              | 21 |

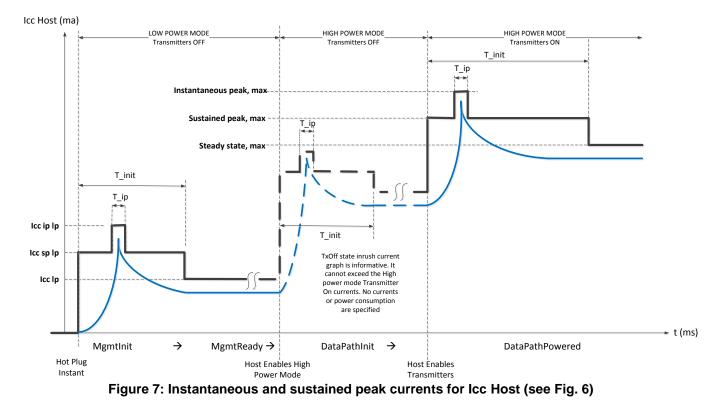

| Figure | 7: Instantaneous and sustained peak currents for Icc Host (see Fig. 6)        | 22 |

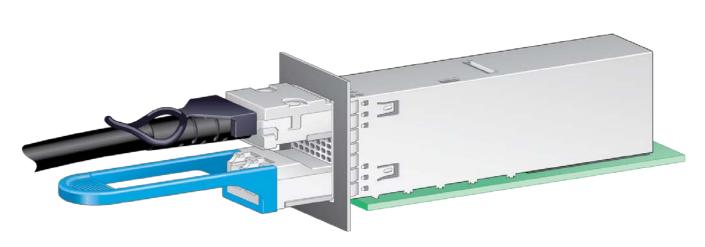

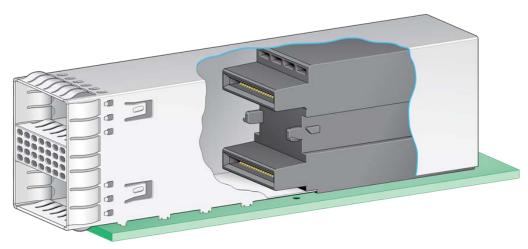

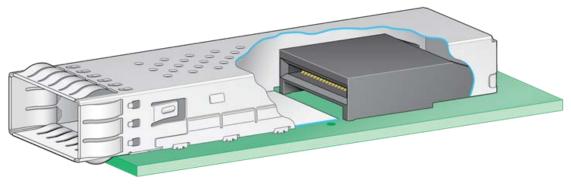

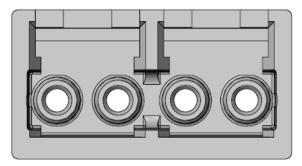

| Figure | 8: 2x1 stacked cage and module                                                | 25 |

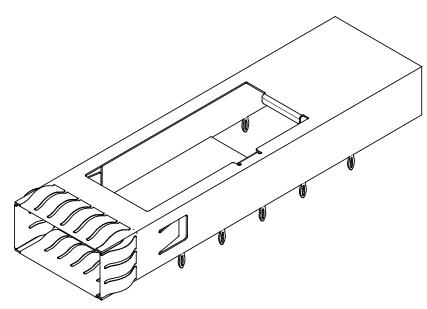

| Figure | 9: Press fit cage for surface mount (SMT) connector                           | 25 |

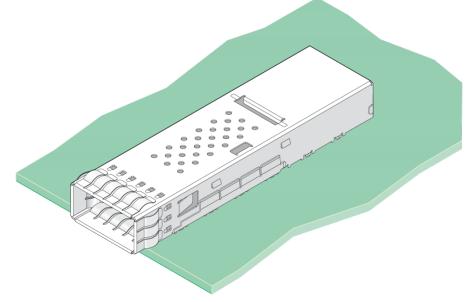

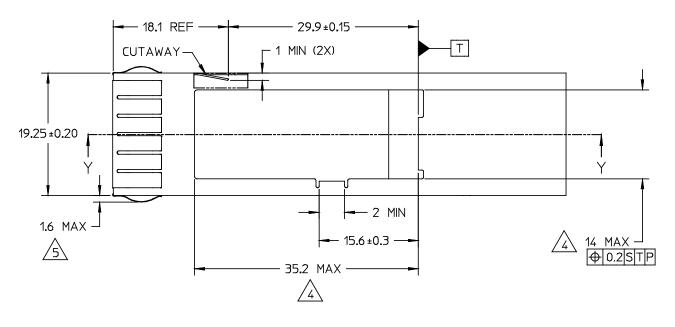

| Figure | 10: Pluggable module                                                          | 26 |

| Figure | 11: 2X1 stacked connector/cage datum descriptions                             | 27 |

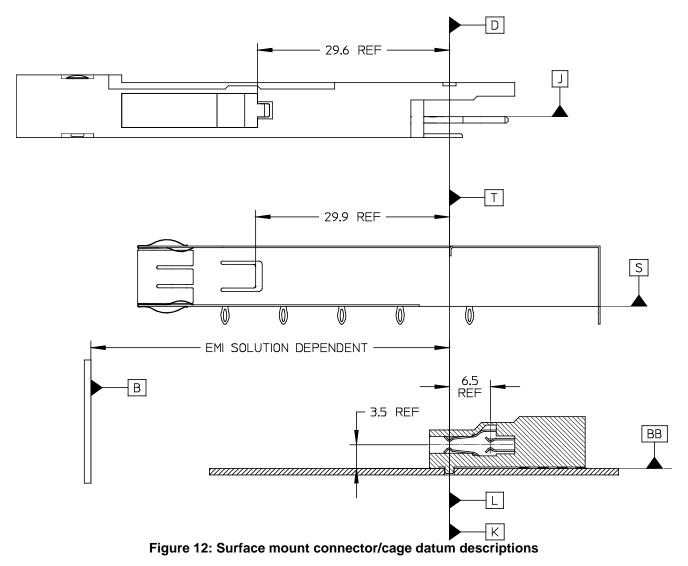

| Figure | 12: Surface mount connector/cage datum descriptions                           | 28 |

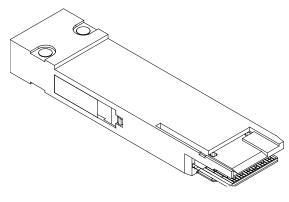

| Figure | 13: Module                                                                    | 29 |

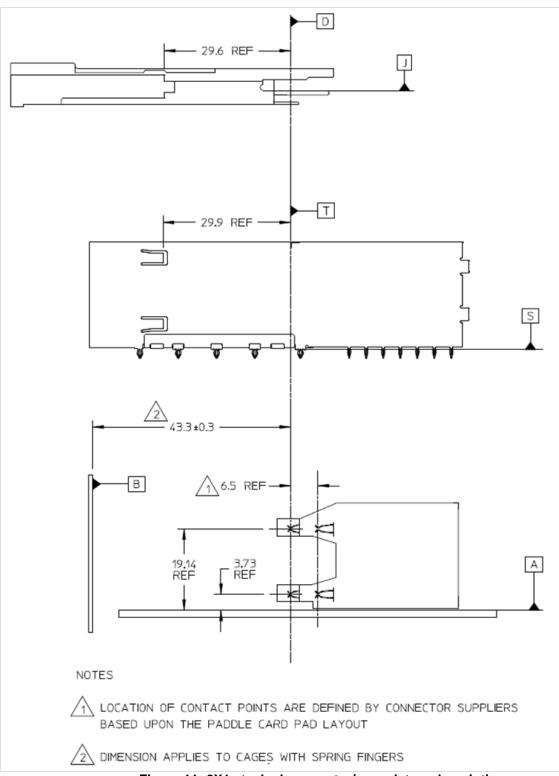

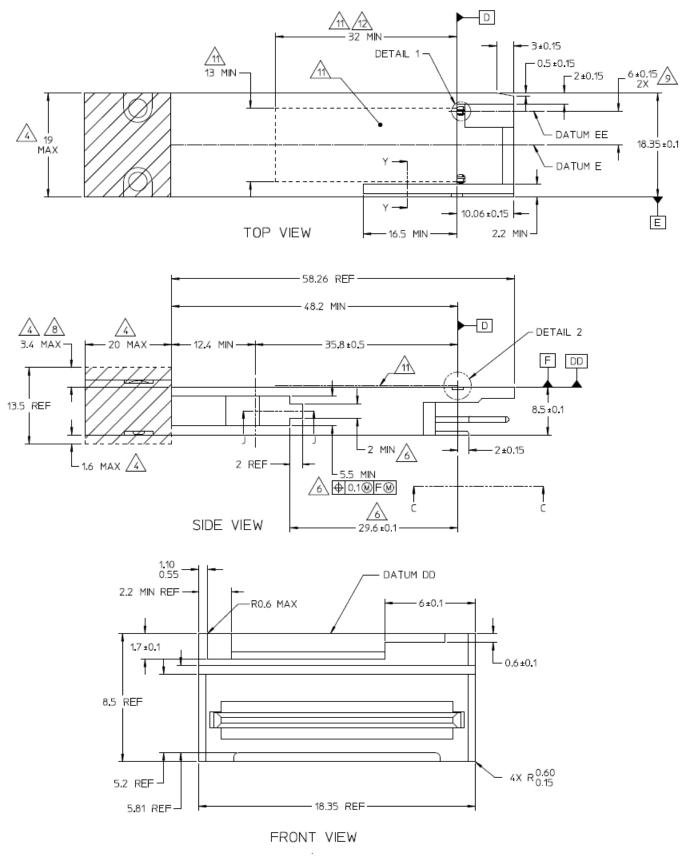

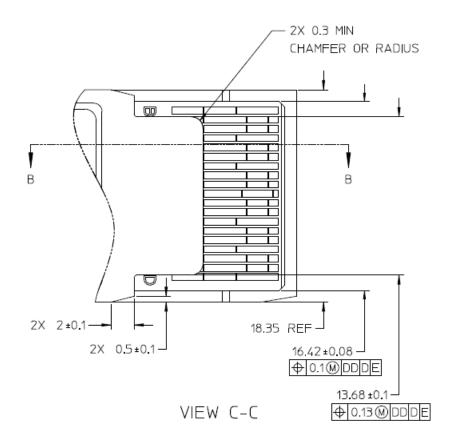

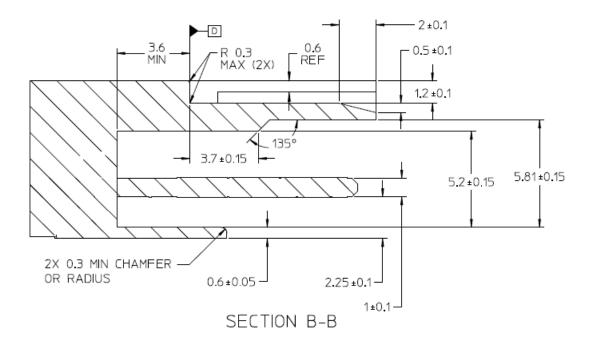

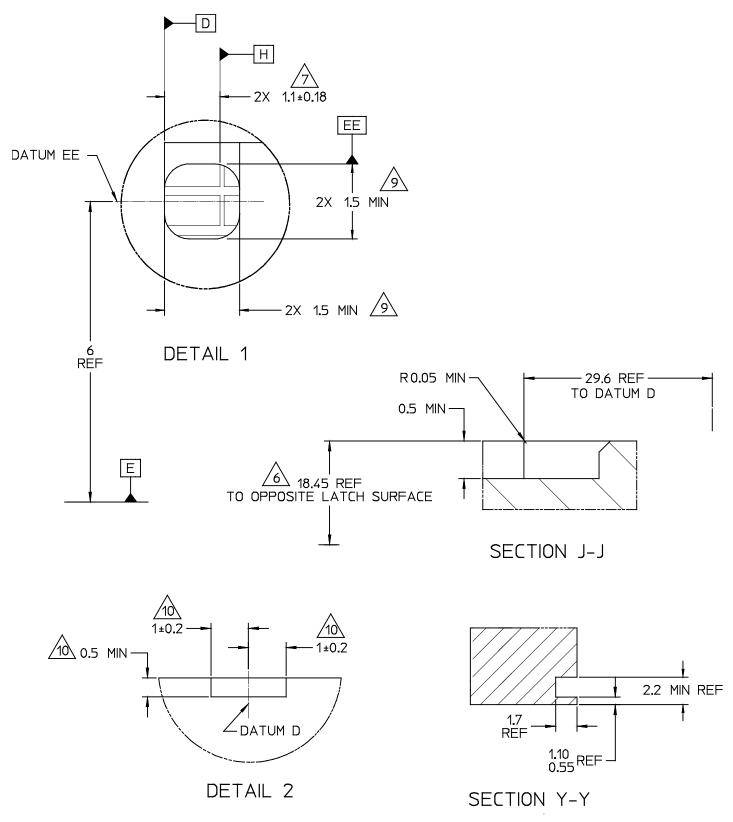

| Figure | 14: Drawing of module                                                         | 30 |

| Figure | 15: Detailed dimension of module                                              | 32 |

|        | 16: Module paddle card dimensions                                             |    |

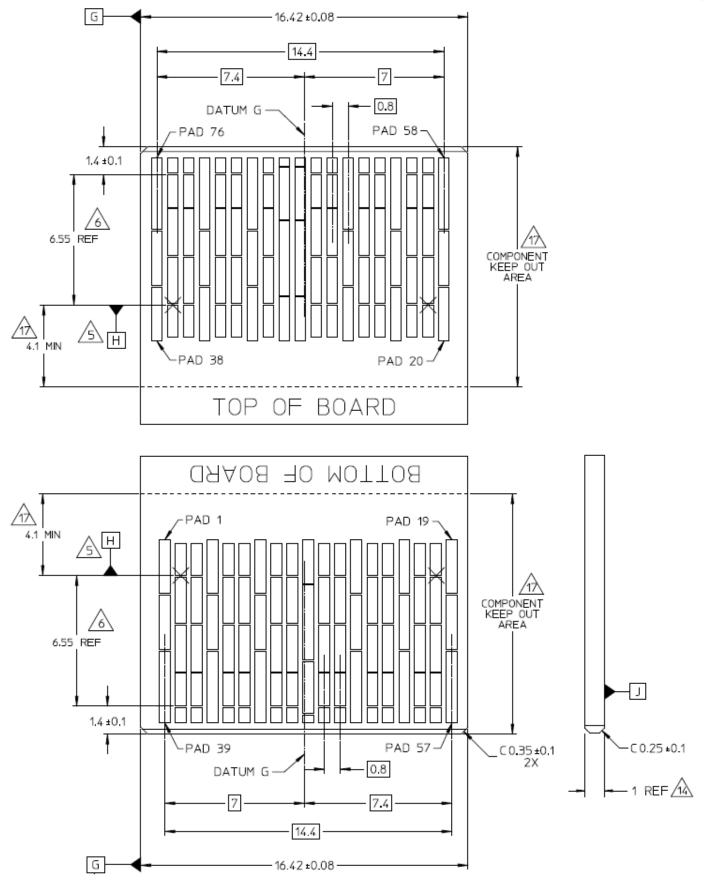

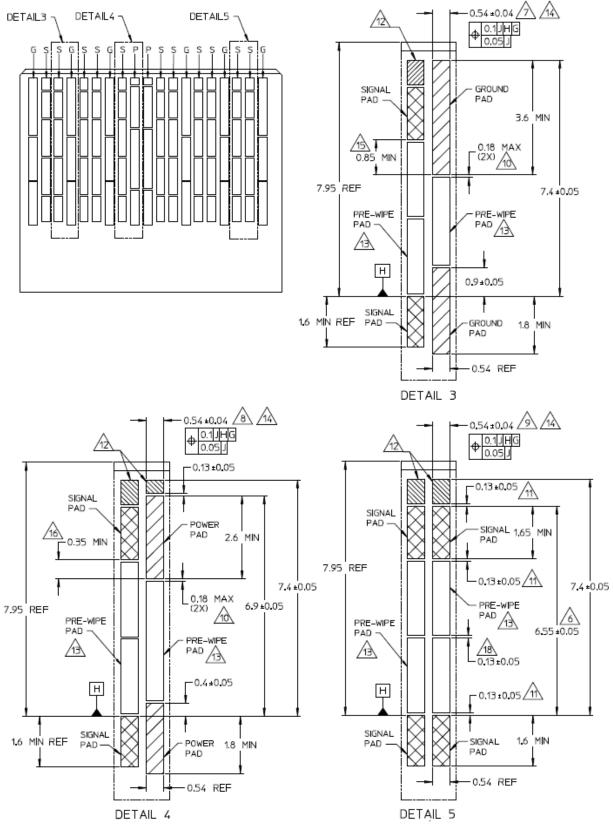

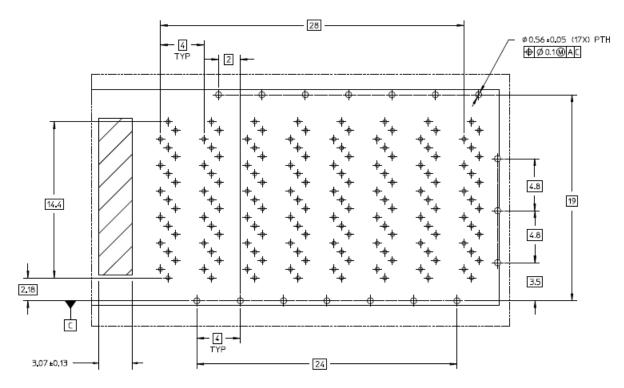

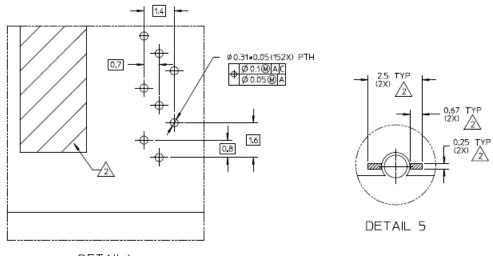

| Figure | 17: Module pad dimensions                                                     | 36 |

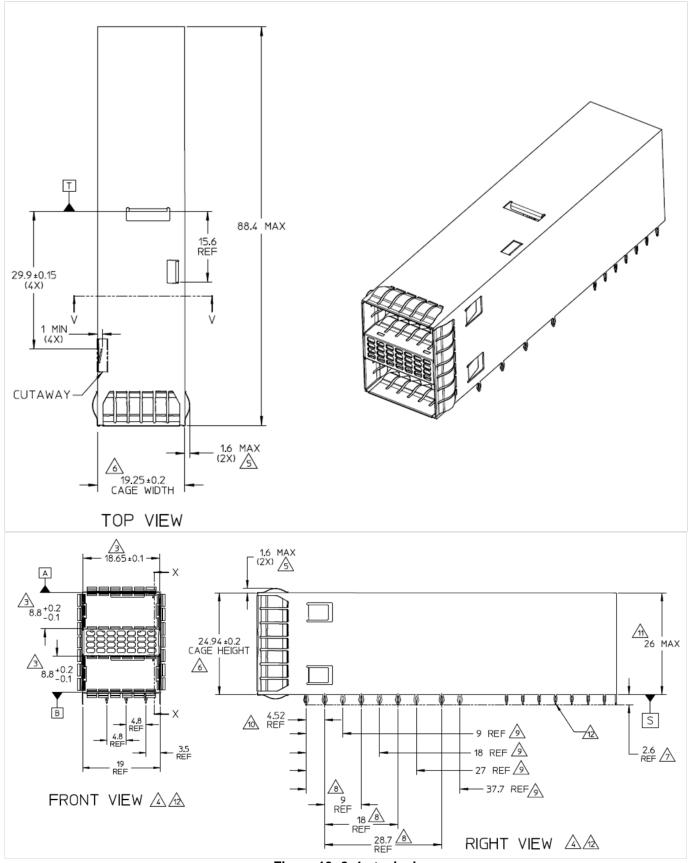

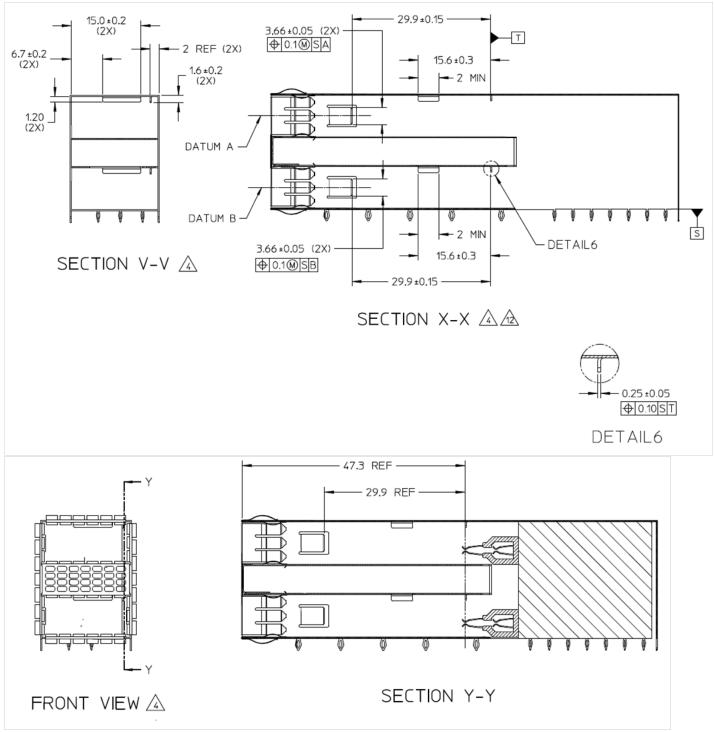

| Figure | 19: 2x1 stacked cage                                                          | 39 |

|        | 20: 2x1 stacked cage dimensions                                               |    |

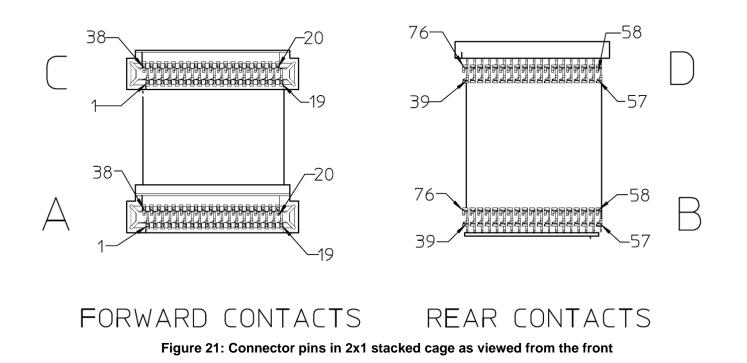

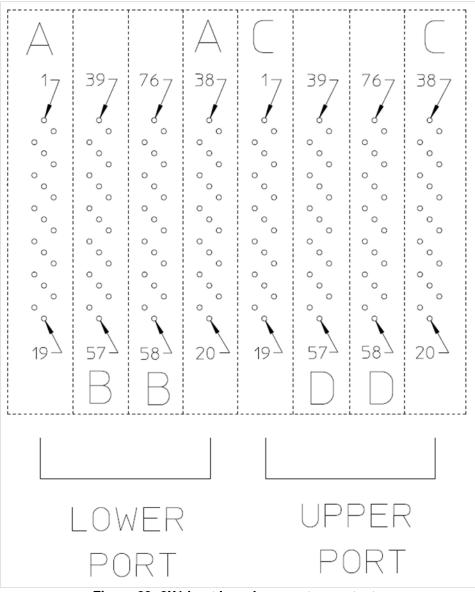

| Figure | 21: Connector pins in 2x1 stacked cage as viewed from the front               | 41 |

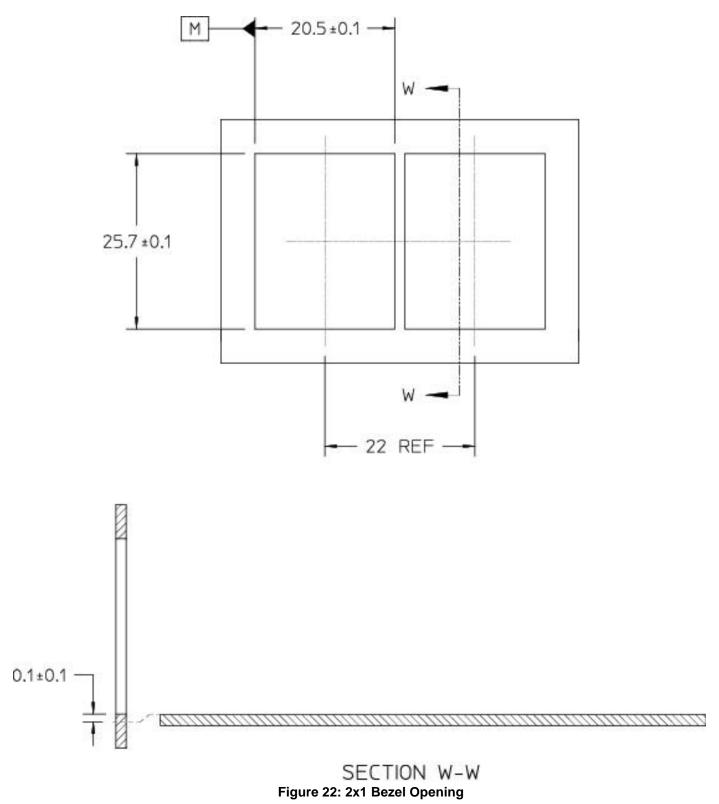

|        | 22: 2x1 Bezel Opening                                                         |    |

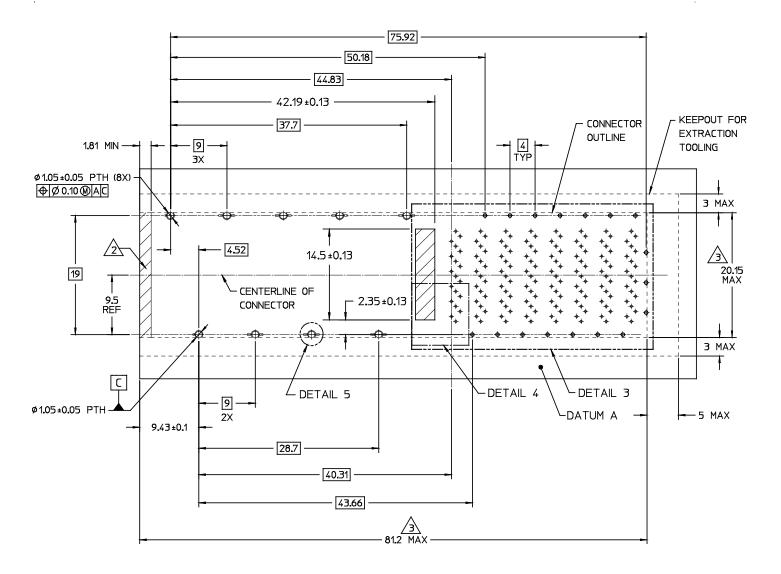

| Figure | 23: 2X1 host board connector contacts                                         | 43 |

| Figure | 24: 2X1 Host PCB Mechanical Layout                                            | 45 |

| Figure | 25: SMT connector in 1xn cage                                                 | 46 |

|        | 26: SMT 1x1 Cage Design                                                       |    |

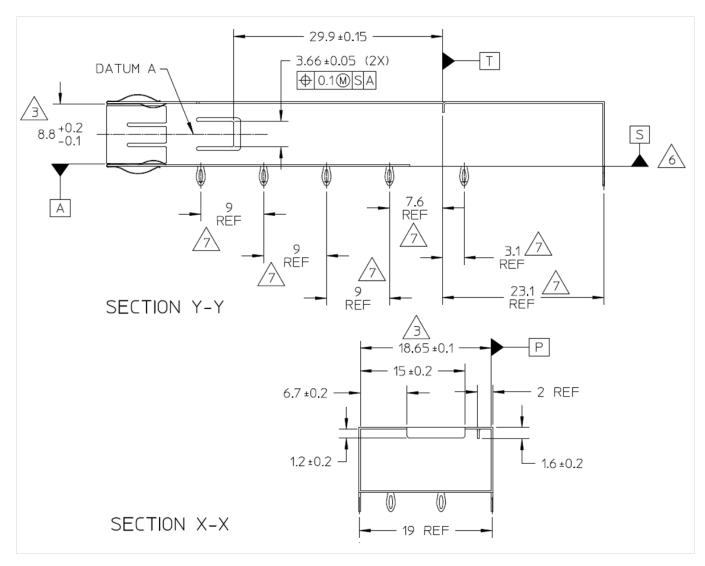

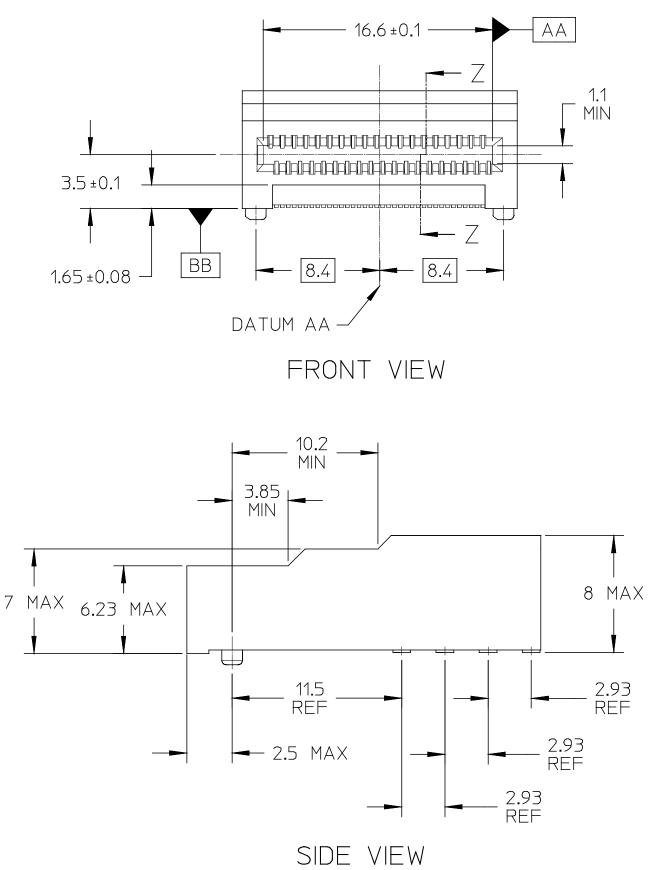

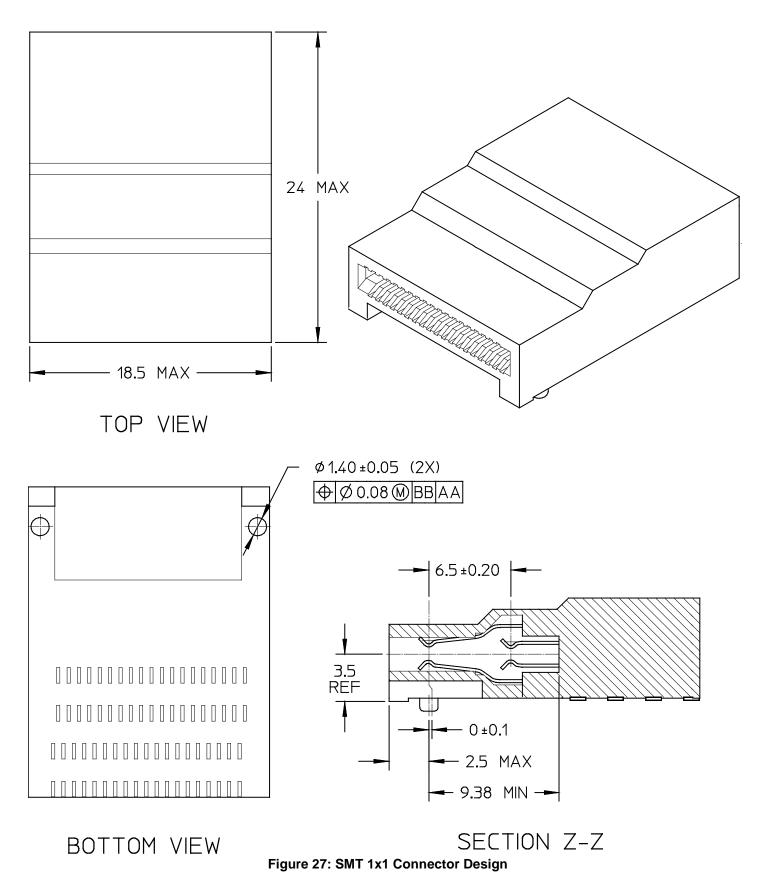

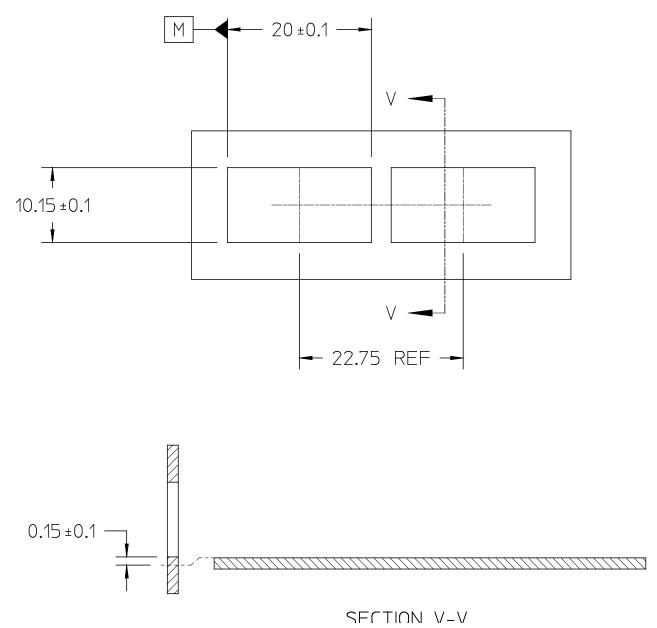

| Figure | 27: SMT 1x1 Connector Design                                                  | 50 |

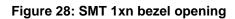

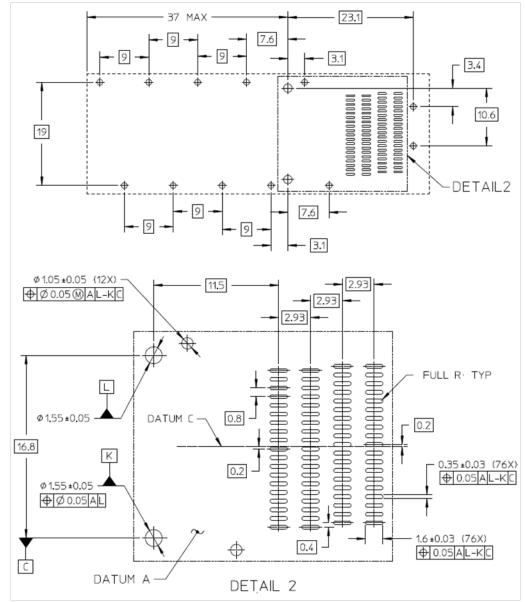

| Figure | 28: SMT 1xn bezel opening                                                     | 51 |

|        | 29: SMT Host PCB Mechanical Layout                                            |    |

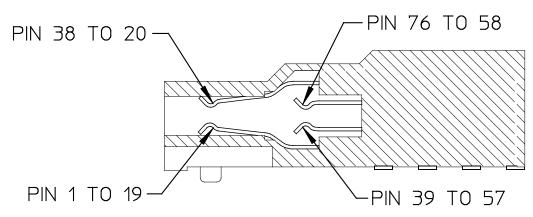

| 0      | 30: SMT Connector and Host PCB Pin Numbers                                    |    |

|        | 31: Optical Media Dependent Interface port assignments                        |    |

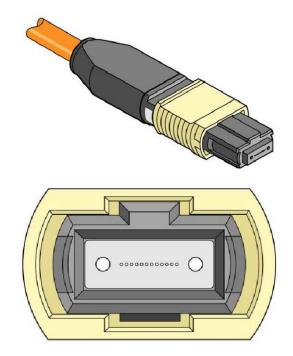

|        | 32: MPO-12 Single Row optical patch cord and module receptacle                |    |

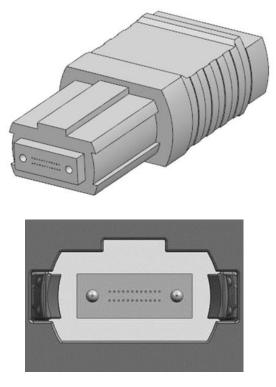

|        | 33: MPO-16 Single Row optical patchcord and module receptacle                 |    |

|        | 34: MPO-12 Two Row optical patchcord and module receptacle                    |    |

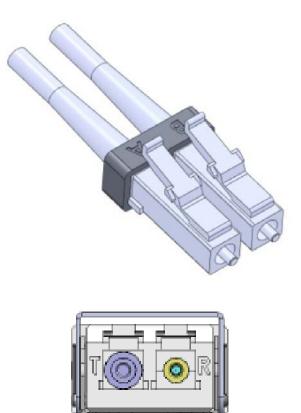

|        | 35: Dual LC optical patchcord and module receptacle                           |    |

|        | 36: Dual CS connector module receptacle (in support of breakout applications) |    |

|        | 37: QSFP-DD Timing Diagram                                                    | 61 |

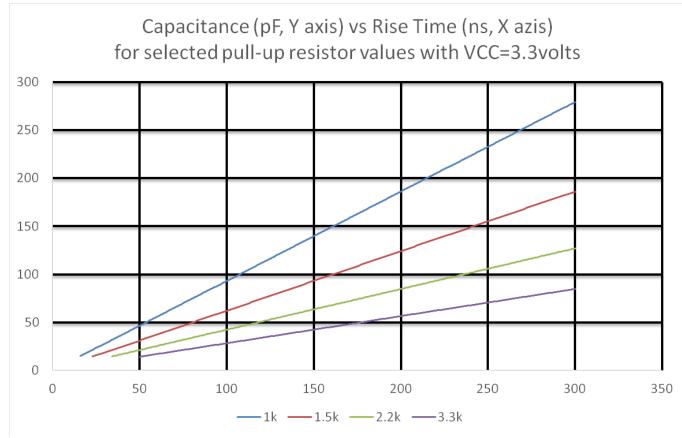

| Figure | 38: SDA and SCL tradeoffs options for pull-up resistor, bus capacitance and   |    |

|        | all times                                                                     |    |

|        | 39 Initialization State Machine                                               |    |

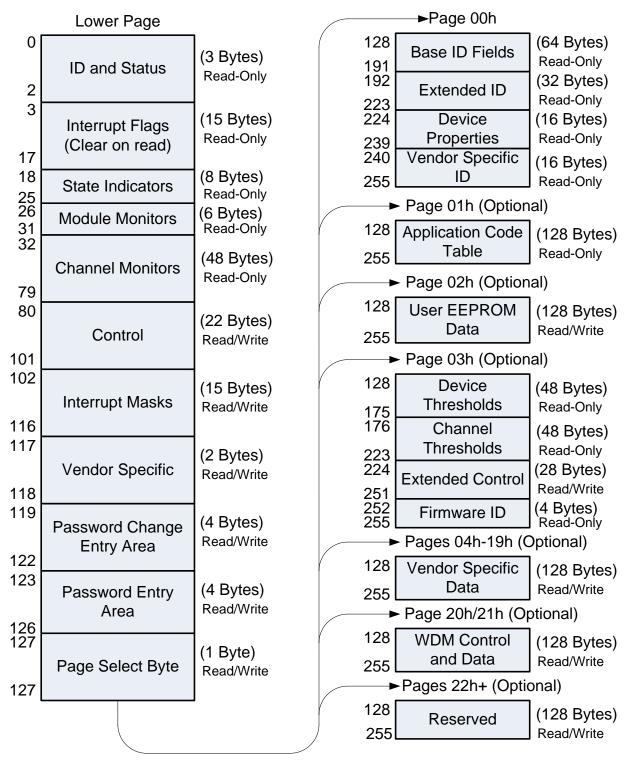

| Figure | 40: QSFP-DD Memory Map                                                        | 73 |

### QSFP-DD 8X Pluggable Transceiver

### 1. Scope

The scope of this specification is the definition of a high density 8-channel (8x) module, cage and connector system. QSFP-DD supports up to 400 Gb/s in aggregate over an 8 x 50 Gb/s electrical interface. The cage and connector design provides backwards compatibility to QSFP28 modules which can be inserted into a QSFP-DD port and connected to 4 of the 8 electrical channels.

#### 1.1 Description of Sections

Section 1 Scope and Purpose

Section 2 Referenced and Related Standards and SFF Specifications

Section 3 Introduction

Section 4 Electrical specifications

Section 5 Mechanical specifications and printed circuit board recommendations

Section 6 Environmental and thermal considerations

Section 7 Management interface, initialization and management register contents.

# 2. References

#### 2.1 Industry Documents

The following interface standards and specifications are relevant to this Specification.

- GR-253-CORE

- IEEE Std 802.3

- IEEE Std 802.3by

- IEEE Std 802.3bs

- IEEE Std 802.3cd

- InfiniBand Architecture Specifications

- FC-РІ-бр

- FC-PI-7

SFF Specifications

- INF-8436 QSFP (Quad SFP) 4 Gbps 4X Transceiver

- SFF-8636 Shielded Cables Common Management Interface

- SFF-8472 Diagnostic Monitoring Interface for Optical Transceivers

- SFF-8661 QSFP+ 4X Pluggable Module

- SFF-8679 QSFP28 4X Base Electrical Specification

CS optical connector specification

- CS-01242017 Can be found at www.QSFP-DD.com

#### 2.2 Sources

This document can be obtained via the www.QSFP-DD.com web site.

# 3 Introduction

This Specification covers the following items:

a) Electrical interfaces including pad assignments for data, control, status and power supplies and host PCB layout requirements.

b) Management interface encompassing features from SFF-8636 with extensions for 8x electrical channels and 400Gb/s data path.

c) Optical interfaces (including optical receptacles and mating fiber plugs for multimode and single-mode duplex and parallel fiber applications). Breakout cable applications are also specified. Optical signaling specifications are not included in this document but are defined in the applicable industry standards.

d) Mechanical specifications including dimensions and tolerances for the connector, cage and module system. Includes details of the requirements for correct mating of the module and host sides of the connector.

e) Thermal requirements

f) Electrostatic discharge (ESD) requirements by reference to industry standard limits and test methods.

This Specification does not cover the following items:

a) Electromagnetic interference (EMI) protection. EMI protection is the responsibility of the implementers of the cages and modules.

### 3.1 Objectives

Electrical signal contact and channel assignments, electrical and power requirements defined in Section 4, optical lane assignments defined in Section 5 and the management interface requirements defined in Section 7 ensure that the pluggable modules and cable assemblies are functionally interchangeable. Dimensions, mounting and insertion requirements defined in Section 5 for the bezel, optical module, cable plug, cage and connector system on a circuit board ensure that these products are mechanically interchangeable.

# 3.2 Applications

This specification defines a common solution for combined eight-channel ports that support Ethernet and/or InfiniBand and/or Fibre Channel requirements. The QSFP-DD interface can support pluggable modules or direct attach cables based on multimode fiber, single mode fiber or copper wires.

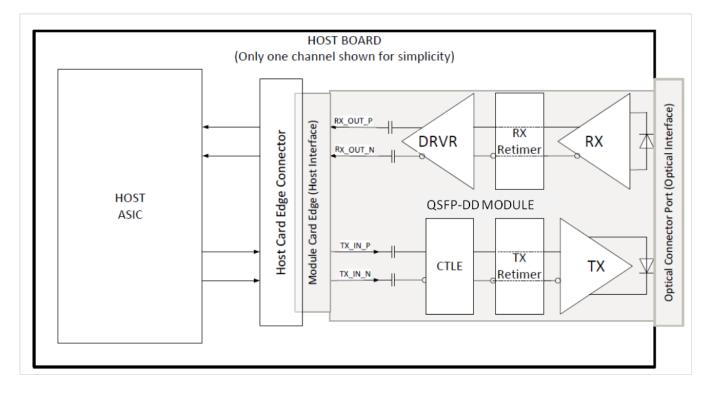

An application reference Model, shown in Figure 1, shows the high-speed data interface between an ASIC and the QSFP-DD module.

### Figure 1: Application Reference Model

Note: For high speed electrical signals the compliance board methodology of IEEE and OIF should be used. Measurements taken with QSFP-DD compliance boards should be corrected for any difference between the loss of these compliance boards and the loss of the compliance boards specified in the standard.

# 4 Electrical Specification

This section contains signal definitions and requirements that are specific to the QSFP-DD module. High-speed signal requirements including compliance points for electrical measurements are defined in the applicable industry standard.

# 4.1 Electrical Connector

The QSFP-DD module edge connector consists of a single paddle card with 38 pads on the top and 38 pads on the bottom of the paddle card for a total of 76 pads. The pads are defined in such a manner so as to accommodate insertion of a QSFP module into a QSFP-DD receptacle. The legacy signal locations are deeper on the paddlecard, so that legacy QSFP module pads only connect to the longer row of connector pins, leaving the short row of connector pins open circuited in a QSFP application.

The pads are designed for a sequenced mating:

First mate - ground pads Second mate - power pads Third mate - signal pads

Because the QSFP-DD module has 2 rows of pads, the additional QSFP-DD pads will have an intermittent connection with the legacy QSFP pins in the connector during the module insertion and removal. The 'legacy' QSFP pads have a 'B' label shown in Table 1 to designate them as the second row of module pads to contact the QSFP-DD connector. The additional QSFP-DD pads have an 'A' label in Table 1 to designate them as the first row of module pads to contact the QSFP-DD pads have first, second and third mate to the connector pins for both insertion and removal. Each of the first, second and third mate connections of the legacy QSFP pads and the respective additional QSFP-DD pads are simultaneous.

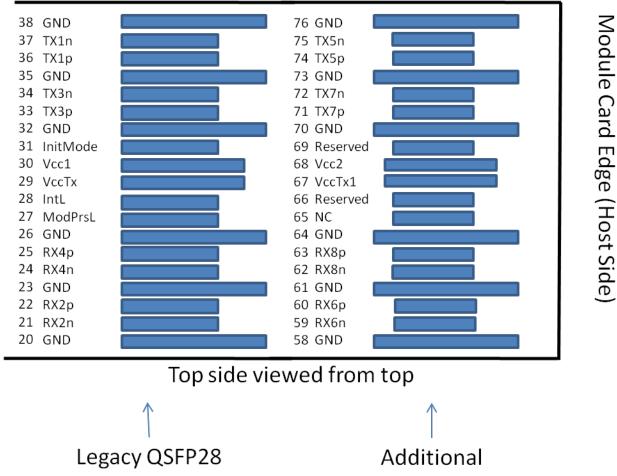

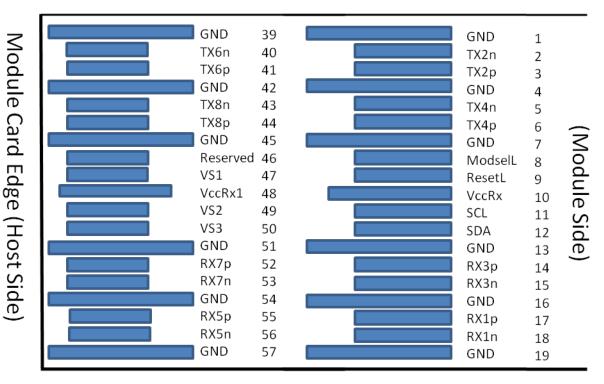

Figure 2 shows the signal symbols and pad numbering for the QSFP-DD module edge connector. The diagram shows the module PCB edge as a top and bottom view. There are 76 pads intended for high speed signals, low speed signals, power and ground connections. Table 1 provides more information about each of the 76 pads. Figure 16 and Figure 17 show pad dimensions . The connector can be integrated into a 2x1 stacked configuration with 2 ports as illustrated in Figure 8 or a surface mount configuration as shown in Figure 9.

For EMI protection the signals from the host connector should be shut off when the QSFP-DD module is not present. Standard board layout practices such as connections to Vcc and GND with vias, use of short and equal-length differential signal lines and 50 Ohm terminations are recommended. The chassis ground (case common) of the QSFP-DD module should be isolated from the module's circuit ground, GND, to provide the equipment designer flexibility regarding connections between external electromagnetic interference shields and circuit ground, GND, of the module.

Pads

QSFP-DD Pads

Bottom side viewed from bottom

|        |                | 1            | Table 1- Pad Function Definition                                                          | 1                             | 1     |

|--------|----------------|--------------|-------------------------------------------------------------------------------------------|-------------------------------|-------|

| Pad    | Logic          | Symbol       | Description                                                                               | Plug<br>Sequence <sup>4</sup> | Notes |

| 1      |                | GND          | Ground                                                                                    | 1B                            | 1     |

| 2      | CML-I          | Tx2n         | Transmitter Inverted Data Input                                                           | 3B                            | 1     |

| 3      | CML-I<br>CML-I | Tx2n<br>Tx2p | Transmitter Non-Inverted Data Input                                                       | 3B<br>3B                      |       |

| 4      | CMT-T          | GND          | Ground                                                                                    | 1B                            | 1     |

| 5      | CML-I          | Tx4n         | Transmitter Inverted Data Input                                                           | 3B                            | 1     |

| 5      |                |              |                                                                                           | 3B                            |       |

| 6<br>7 | CML-I          | Tx4p         | Transmitter Non-Inverted Data Input                                                       | -                             | 1     |

|        | T 77000T T     | GND          | Ground                                                                                    | 1B                            | 1     |

| 8      | LVTTL-I        | ModSelL      | Module Select                                                                             | 3B                            |       |

| 9      | LVTTL-I        | ResetL       | Module Reset                                                                              | 3B                            | 0     |

| 10     |                | VccRx        | +3.3V Power Supply Receiver                                                               | 2B                            | 2     |

| 11     | LVCMOS-<br>I/O | SCL          | 2-wire serial interface clock                                                             | 3B                            |       |

| 12     | LVCMOS-<br>I/O | SDA          | 2-wire serial interface data                                                              | 3В                            |       |

| 13     |                | GND          | Ground                                                                                    | 1B                            | 1     |

| 14     | CML-O          | Rx3p         | Receiver Non-Inverted Data Output                                                         | 3B                            |       |

| 15     | CML-O          | Rx3n         | Receiver Inverted Data Output                                                             | 3B                            |       |

| 16     |                | GND          | Ground                                                                                    | 1B                            | 1     |

| 17     | CML-O          | Rx1p         | Receiver Non-Inverted Data Output                                                         | 3B                            |       |

| 18     | CML-O          | Rx1n         | Receiver Inverted Data Output                                                             | 3B                            |       |

| 19     |                | GND          | Ground                                                                                    | 1B                            | 1     |

| 20     |                | GND          | Ground                                                                                    | 1B                            | 1     |

| 21     | CML-O          | Rx2n         | Receiver Inverted Data Output                                                             | 3B                            |       |

| 22     | CML-O          | Rx2p         | Receiver Non-Inverted Data Output                                                         | 3B                            |       |

| 23     |                | GND          | Ground                                                                                    | 1B                            | 1     |

| 24     | CML-O          | Rx4n         | Receiver Inverted Data Output                                                             | 3B                            |       |

| 25     | CML-O          | Rx4p         | Receiver Non-Inverted Data Output                                                         | 3B                            |       |

| 26     |                | GND          | Ground                                                                                    | 1B                            | 1     |

| 27     | LVTTL-O        | ModPrsL      | Module Present                                                                            | 3B                            |       |

| 28     | LVTTL-O        | IntL         | Interrupt                                                                                 | 3B                            |       |

| 29     |                | VccTx        | +3.3V Power supply transmitter                                                            | 2B                            | 2     |

| 30     |                | Vccl         | +3.3V Power supply                                                                        | 2B                            | 2     |

| 31     | LVTTL-I        | InitMode     | Initialization mode; In legacy QSFP<br>applications, the InitMode pad is called<br>LPMODE | 3В                            |       |

| 32     |                | GND          | Ground                                                                                    | 1B                            | 1     |

| 33     | CML-I          | Tx3p         | Transmitter Non-Inverted Data Input                                                       | 3B                            |       |

| 34     | CML-I          | Tx3n         | Transmitter Inverted Data Input                                                           | 3B                            |       |

| 35     |                | GND          | Ground                                                                                    | 1B                            | 1     |

| 36     | CML-I          | Txlp         | Transmitter Non-Inverted Data Input                                                       | 3B                            |       |

| 37     | CML-I          | Txln         | Transmitter Inverted Data Input                                                           | 3B                            |       |

| 38     |                | GND          | Ground                                                                                    | 1B                            | 1     |

# **Table 1- Pad Function Definition**

| Pad                 | Logic                          | Symbol                                   | Description                                                                                                                                                         | Plug                       | Notes           |  |  |

|---------------------|--------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------|--|--|

|                     | 2                              | -                                        | -                                                                                                                                                                   | Sequence <sup>4</sup>      |                 |  |  |

| 39                  |                                | GND                                      | GND Ground                                                                                                                                                          |                            |                 |  |  |

| 40                  | CML-I                          | Тхбп                                     | Transmitter Inverted Data Input 3A                                                                                                                                  |                            |                 |  |  |

| 41                  | CML-I                          | Тхбр                                     | 3A                                                                                                                                                                  |                            |                 |  |  |

| 42                  |                                | GND                                      | Transmitter Non-Inverted Data Input<br>Ground                                                                                                                       | 1A                         | 1               |  |  |

| 43                  | CML-I                          | Tx8n                                     | Transmitter Inverted Data Input                                                                                                                                     | 3A                         | -               |  |  |

| 44                  | CML-I                          | Tx8p                                     | Transmitter Non-Inverted Data Input                                                                                                                                 | 3A                         |                 |  |  |

| 45                  |                                | GND                                      | 1A                                                                                                                                                                  | 1                          |                 |  |  |

| 46                  |                                | Reserved                                 | Ground<br>For future use                                                                                                                                            | 3A                         | 3               |  |  |

| 47                  |                                | VS1                                      | Module Vendor Specific 1                                                                                                                                            | 3A                         | 3               |  |  |

| 48                  |                                | VccRx1                                   | 3.3V Power Supply                                                                                                                                                   | 2A                         | 2               |  |  |

| 49                  |                                | VCCRXI<br>VS2                            | Module Vendor Specific 2                                                                                                                                            | 3A                         | 3               |  |  |

| 50                  |                                | VS2<br>VS3                               | Module Vendor Specific 3                                                                                                                                            | 3A                         | 3               |  |  |

| 51                  |                                | GND                                      | Ground                                                                                                                                                              | 1A                         | 1               |  |  |

| 52                  | CML-0                          | -                                        |                                                                                                                                                                     | 3A                         | 1               |  |  |

|                     |                                | Rx7p                                     | Receiver Non-Inverted Data Output                                                                                                                                   | -                          |                 |  |  |

| 53                  | CML-0                          | Rx7n                                     | Receiver Inverted Data Output                                                                                                                                       | 3A                         | 1               |  |  |

| 54                  | <i>съ съ</i> .                 | GND                                      | Ground                                                                                                                                                              | 1A                         | 1               |  |  |

| 55                  | CML-O                          | Rx5p                                     | Receiver Non-Inverted Data Output                                                                                                                                   | 3A                         |                 |  |  |

| 56                  | CML-O                          | Rx5n                                     | Receiver Inverted Data Output                                                                                                                                       | 3A                         | -               |  |  |

| 57                  |                                | GND                                      | Ground                                                                                                                                                              | 1A                         | 1               |  |  |

| 58                  |                                | GND                                      | Ground                                                                                                                                                              | 1A                         | 1               |  |  |

| 59                  | CML-O                          | Rхбп                                     | Receiver Inverted Data Output                                                                                                                                       | 3A                         |                 |  |  |

| 60                  | CML-O                          | Rхбр                                     | Receiver Non-Inverted Data Output                                                                                                                                   | 3A                         |                 |  |  |

| 61                  |                                | GND                                      | Ground                                                                                                                                                              | 1A                         | 1               |  |  |

| 62                  | CML-O                          | Rx8n                                     | Receiver Inverted Data Output                                                                                                                                       | 3A                         |                 |  |  |

| 63                  | CML-O                          | Rx8p                                     | Receiver Non-Inverted Data Output                                                                                                                                   | 3A                         |                 |  |  |

| 64                  |                                | GND                                      | Ground                                                                                                                                                              | 1A                         | 1               |  |  |

| 65                  |                                | NC                                       | No Connect                                                                                                                                                          | 3A                         | 3               |  |  |

| 66                  |                                | Reserved                                 | For future use                                                                                                                                                      | 3A                         | 3               |  |  |

| 67                  |                                | VccTx1                                   | 3.3V Power Supply                                                                                                                                                   | 2A                         | 2               |  |  |

| 68                  |                                | Vcc2                                     | 3.3V Power Supply                                                                                                                                                   | 2A                         | 2               |  |  |

| 69                  |                                | Reserved                                 | For Future Use                                                                                                                                                      | 3A                         | 3               |  |  |

| 70                  |                                | GND                                      | Ground                                                                                                                                                              | 1A                         | 1               |  |  |

| 71                  | CML-I                          | Tx7p                                     | Transmitter Non-Inverted Data Input                                                                                                                                 | 3A                         | -               |  |  |

| 72                  | CML-I                          | Tx7n                                     | Transmitter Inverted Data Input                                                                                                                                     | 3A                         |                 |  |  |

| 73                  |                                | GND                                      | Ground                                                                                                                                                              | 1A                         | 1               |  |  |

| 74                  | CMT T                          | -                                        |                                                                                                                                                                     | -                          | 1               |  |  |

| 75                  | CML-I                          | Tx5p                                     | Transmitter Non-Inverted Data Input                                                                                                                                 | 3A<br>3A                   |                 |  |  |

| 76                  | CML-I                          | Tx5n                                     | Transmitter Inverted Data Input<br>Ground                                                                                                                           |                            | 1               |  |  |

| Note<br>comm        | on withi                       | n the QSFP-                              | ommon ground (GND)for all signals and suppl<br>DD module and all module voltages are refe<br>vise noted. Connect these directly to the h                            | renced to t                | his             |  |  |

|                     | on ground                      |                                          |                                                                                                                                                                     |                            |                 |  |  |

|                     |                                | -                                        | Vcc1, Vcc2, VccTx and VccTx1 shall be appl                                                                                                                          | ied conquer                | ontly           |  |  |

| Requ<br>in T        | irements<br>able 4.            | defined fo<br>VccRx, Vcc                 | or the host side of the Host Card Edge Conn<br>Rx1, Vcc1, Vcc2, VccTx and VccTx1 may be i                                                                           | ector are l<br>nternally   | isted           |  |  |

|                     |                                |                                          | odule in any combination. The connector Vcc                                                                                                                         | pins are e                 | ach             |  |  |

|                     |                                |                                          | rrent of 1000 mA.                                                                                                                                                   |                            |                 |  |  |

| ohms<br>the<br>is g | to grou<br>module.<br>reater t | nd on the h<br>Vendor spe<br>han 10 kOhm | eific, Reserved and No Connect pins may be<br>nost. Pad 65 (No Connect) shall be left un<br>ecific and Reserved pads shall have an impe<br>ns and less than 100 pF. | connected w<br>dance to GN | ithin<br>D that |  |  |

|                     |                                |                                          | specifies the mating sequence of the host c                                                                                                                         |                            |                 |  |  |

|                     |                                |                                          | s 1A, 2A, 3A, 1B, 2B, 3B. (see Figure 2 for                                                                                                                         |                            |                 |  |  |

| Sequ                | ence 1A,                       |                                          | . make, then break contact with additional<br>nen occur simultaneously, followed by 2A, 2                                                                           |                            |                 |  |  |

| 3A,3                | в.                             |                                          |                                                                                                                                                                     |                            |                 |  |  |

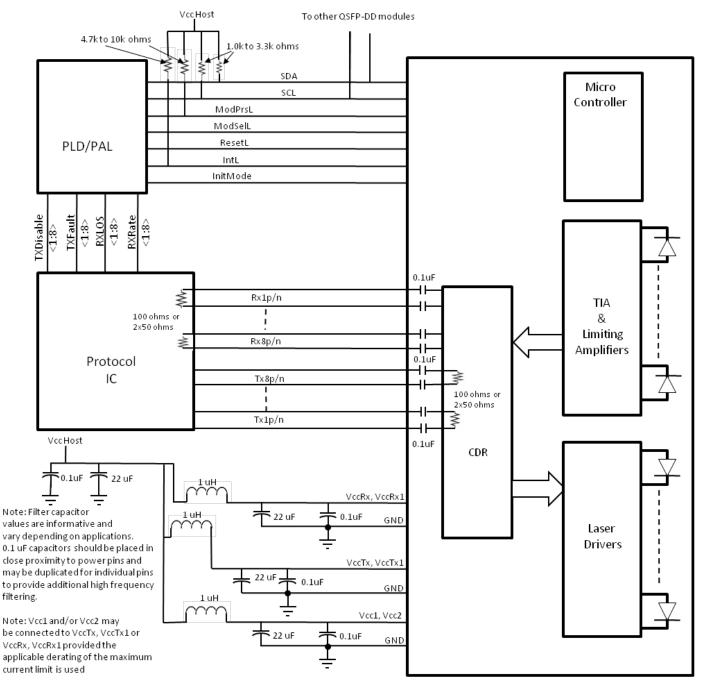

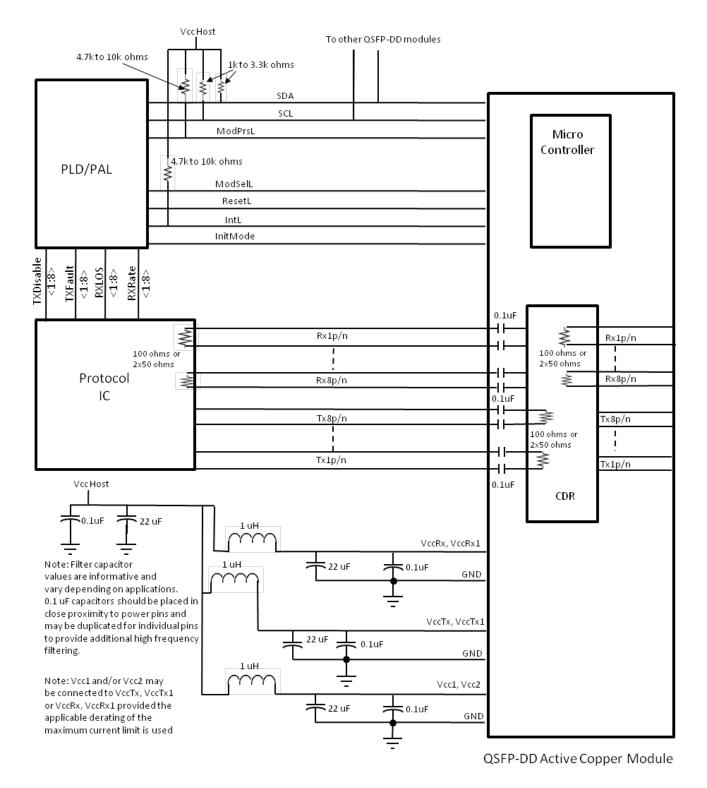

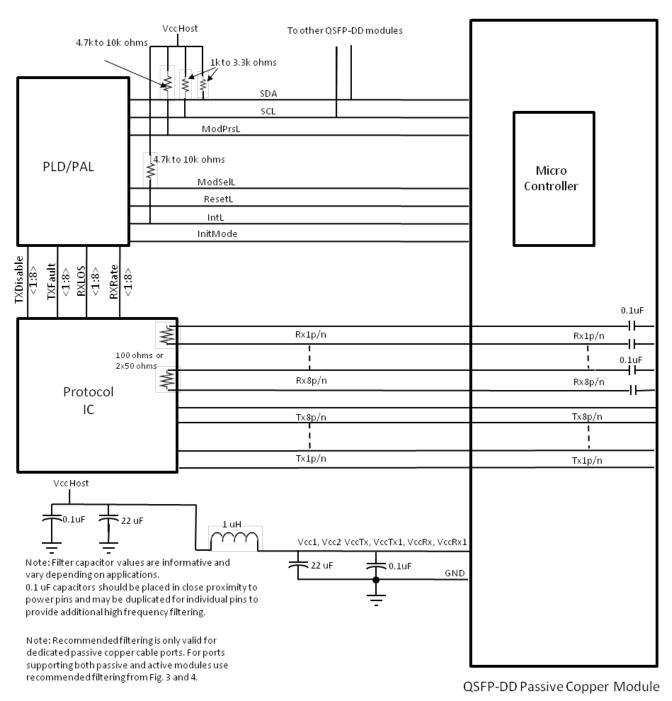

Figure 3, Figure 4 and Figure 5 show examples of QSFP-DD host PCB schematics with connections to CDR and control ICs. An 8 wide electrical/optical interface is shown. Note alternate electrical/optical interfaces are supported using optical multiplexing (WDM) or electrical multiplexing.

QSFP-DD Optical Module

Figure 3: Example QSFP-DD Host Board Schematic For Optical Modules

Figure 4: Example QSFP-DD Host Board Schematic for active copper cables

### 4.1.1 Low Speed Electrical Hardware Signals

In addition to the 2-wire serial interface the module has the following low speed signals for control and status:

ModSelL ResetL InitMode ModPrsL IntL

#### 4.1.1.1 ModSelL

The ModSelL is an input signal that must be pulled to Vcc in the QSFP-DD module. When held low by the host, the module responds to 2-wire serial communication commands. The ModSelL allows the use of multiple QSFP-DD modules on a single 2-wire interface bus. When ModSelL is "High", the module shall not respond to or acknowledge any 2-wire interface communication from the host.

In order to avoid conflicts, the host system shall not attempt 2-wire interface communications within the ModSelL de-assert time after any QSFP-DD modules are deselected. Similarly, the host must wait at least for the period of the ModSelL assert time before communicating with the newly selected module. The assertion and de-asserting periods of different modules may overlap as long as the above timing requirements are met.

#### 4.1.1.2 ResetL

The ResetL signal shall be pulled to Vcc in the module. A low level on the ResetL signal for longer than the minimum pulse length (t\_Reset\_init) (See Table 13) initiates a complete module reset, returning all user module settings to their default state.

#### 4.1.1.3 InitMode

InitMode is an input signal. The InitMode signal must be pulled up to Vcc in the QSFP-DD module. The InitMode signal allows the host to define whether the QSFP-DD module will initialize under host software control (InitMode asserted High) or module hardware control (InitMode deasserted Low). Under host software control, the module shall remain in Low Power Mode until software enables the transition to High Power Mode, as defined in Section 7.5. Under hardware control (InitMode de-asserted Low), the module may immediately transition to High Power Mode after the management interface is initialized. The host shall not change the state of this signal while the module is present. In legacy QSFP applications, this signal is named LPMode. See SFF-8679 for signal description.

#### 4.1.1.4 ModPrsL

ModPrsL must be pulled up to Vcc Host on the host board and grounded in the module. The ModPrsL is asserted "Low" when the module is inserted and deasserted "High" when the module is physically absent from the host connector.

#### 4.1.1.5 IntL

IntL is an output signal. The IntL signal is an open collector output and must be pulled to Vcc Host on the host board. When the IntL signal is asserted Low it indicates a change in module state, a possible module operational fault or a status critical to the host system. The host identifies the source of the interrupt using the 2-wire serial interface. The IntL signal is deasserted "High" after all set interrupt flags are read.

#### 4.1.2 Low Speed Electrical Specification

Low speed signaling other than the SCL and SDA interface is based on Low Voltage TTL (LVTTL) operating at Vcc. Vcc refers to the generic supply voltages of VccTx, VccRx, Vcc host or Vcc1. Hosts shall use a pull-up resistor connected to Vcc host on each of the 2-wire interface SCL (clock), SDA (data), and all low speed status outputs. The SCL and SDA is a hot plug interface that may support a bus topology. During module insertion or removal, the module may implement a pre-charge circuit which prevents corrupting data transfers from other modules that are already using the bus.

Note: Timing diagrams for SCL and SDA are included in Section 7.1.2 Management Interface Timing Specification.

The QSFP-DD low speed electrical specifications are given in Table 2. This specification ensures compatibility between host bus masters and the 2-wire interface.

| Parameter           | Symbol | Min     | Max     | Unit | Condition                      |

|---------------------|--------|---------|---------|------|--------------------------------|

| SCL and SDA         | VOL    | 0       | 0.4     | V    | IOL(max) = 3.0mA               |

|                     | VOH    | Vcc-0.5 | Vcc+0.3 | V    |                                |

| SCL and SDA         | VIL    | -0.3    | Vcc*0.3 | V    |                                |

|                     | VIH    | VCC*0.7 | Vcc+0.5 | V    |                                |

| Capacitance for SCL | Ci     |         | 14      | pF   |                                |

| and SDA I/O signal  |        |         |         |      |                                |

| Total bus           | Cb     |         | 100     | pF   | 3.0 k Ohms Pullup              |

| capacitive load for |        |         |         |      | resistor, max                  |

| SCL and SDA         |        |         | 200     | pF   | 1.6 k Ohms pullup              |

|                     |        |         |         |      | resistor max                   |

| InitMode, ResetL    | VIL    | -0.3    | 0.8     | V    | Iin <=125 uA for               |

| and ModSelL         |        |         |         |      | 0V <vin,vcc< td=""></vin,vcc<> |

|                     | VIH    | 2       | VCC+0.3 | V    |                                |

| ModPrsL and IntL    | VOL    | 0       | 0.4     | V    | IOL=2.0mA                      |

|                     | VOH    | VCC-0.5 | VCC+0.3 | V    |                                |

| Table 2- Low Speed Control and Sense Sign | nals |

|-------------------------------------------|------|

|-------------------------------------------|------|

### 4.1.3 High Speed Electrical Specification

For detailed electrical specifications see the appropriate specification, e.g. 802.3ba Annex 86A, 802.3bs Annex 120E, FC-PI-6, FC-PI-7, OIF-CEI-28G-VSR, OIF-CEI-56G-VSR or the InfiniBand specification.

Partial or complete squelch specifications may be provided in the appropriate specification. Where squelch is not fully defined by the appropriate specification, the recommendations of the following subsections 4.1.3.1 and 4.1.3.2 may be used.

#### 4.1.3.1 Rx(n)(p/n)

Rx(n)(p/n) are QSFP-DD module receiver data outputs. Rx(n)(p/n) are AC-coupled 100 Ohm differential lines that should be terminated with 100 Ohm differentially at the Host ASIC(SerDes). The AC coupling is inside the QSFP-DD module and not required on the Host board. When properly terminated, the differential voltage swing shall be less than or equal to 900 mVpp or the relevant standard, whichever is less.

Output squelch for loss of optical input signal, hereafter RX Squelch, is required and shall function as follows. In the event of the Rx input signal on any optical port becoming equal to or less than the level required to assert LOS, then the receiver output(s) associated with that Rx port shall be squelched. A single Rx optical port can be associated with more than one Rx output as shown in Section 5.10.4. In the squelched state output impedance levels are maintained while the differential voltage amplitude shall be less than 50 mVpp.

In normal operation the default case has RX Squelch active. Rx Squelch can be deactivated using Rx Squelch Disable through the 2-wire serial interface.

### 4.1.3.2 Tx(n)(p/n)

Tx(n)(p/n) are QSFP-DD module transmitter data inputs. They are AC-coupled 100 Ohm differential lines with 100 Ohm differential terminations inside the QSFP-DD optical module. The AC coupling is implemented inside the QSFP-DD optical module and not required on the Host board.

Output squelch for loss of electrical signal, hereafter Tx Squelch, is an optional function. Where implemented it shall function as follows. In the event of the differential, peak-to-peak electrical signal amplitude on any electrical input channel becoming less than 50 mVpp, then the transmitter optical output associated with that electrical input channel shall be squelched and the associated TxLOS flag set. If multiple electrical input channels are associated with the same optical output channel,

the loss of any of the incoming electrical input channels causes the optical output channel to be squelched.

For applications, e.g. Ethernet, where the transmitter off condition is defined in terms of average power, squelching by disabling the transmitter is recommended and for applications, e.g. InfiniBand, where the transmitter off condition is defined in terms of OMA, squelching the transmitter by setting the OMA to a low level is recommended.

In module operation, where Tx Squelch is implemented, the default case has Tx Squelch active. Tx Squelch can be deactivated using Tx Squelch Disable through the 2-wire serial interface. Tx Squelch is an optional function. If TX squelch is implemented, the disable squelch must be provided.

#### 4.2 Power Requirements

The power supply has six designated pins, VccTx, VccTx1, Vcc1, Vcc2, VccRx, VccRx1 in the connector. Vcc1 and Vcc2 are used to supplement VccTx, VccTx1, VccRx or VccRx1 at the discretion of the module vendor. Power is applied concurrently to these pins.

A host board together with the QSFP-DD module(s) forms an integrated power system. The host supplies stable power to the module. The module limits electrical noise coupled back into the host system and limits inrush charge/current during hot plug insertion.

All power supply requirements in Table 4 shall be met at the maximum power supply current. No power sequencing of the power supply is required of the host system since the module sequences the contacts in the order of ground, supply and signals during insertion.

#### 4.2.1 Power Classes and Maximum Power Consumption

There are two power modes; Low Power Mode and High Power Mode. Modules are either in Low Power Mode or High Power Mode as defined in Table 4 and Section 7.

Since different classes of modules exist with pre-defined maximum power consumption limits, it is necessary to avoid exceeding the system power supply limits and cooling capacity when a module is inserted into a system designed to only accommodate lower power modules. It is recommended that the host implement the state machine recommended in Section 7 and identify the power class of the module before allowing the module to go into high power mode.

Power levels associated with classifications of modules are shown in Table 3.

|             | Someation     |

|-------------|---------------|

| Power Class | Max Power (W) |

| 1           | 1.0           |

| 2           | 3.5           |

| 3           | 7.0           |

| 4           | 8.0           |

| 5           | 10            |

| 6           | 12            |

| 7           | 14            |

| 8           | >14           |

#### Table 3- Power Classification

In general, the higher power classification levels are associated with higher data rates and longer reaches. The system designer is responsible for ensuring that the maximum case temperature does not exceed the case temperature requirements.

#### 4.2.2 Host Board Power Supply Filtering

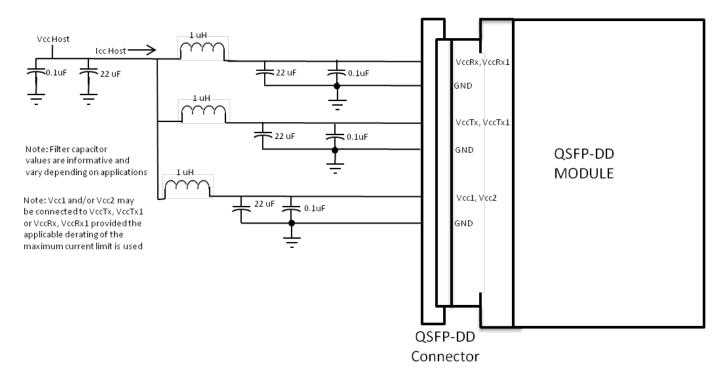

The host board should use the power supply filtering equivalent to that shown in Figure 6.

#### Figure 6: Recommended Host Board Power Supply Filtering

Any voltage drop across a filter network on the host is counted against the host DC set point accuracy specification. Inductors with DC Resistance of less than 0.1 Ohm should be used in order to maintain the required voltage at the Host Card Edge Connector. It is recommended that the 22 uF capacitors each have an equivalent series resistance of 0.22 ohm.

The specifications for the power supply are shown in Table 4. The limits in Table 4 apply to the combined current that flows through all inductors in the power supply filter (represents ICC host in Figure 6). The test method for measuring inrush current can be found in http://cp.literature.agilent.com/litweb/pdf/5991-2778EN.pdf.

#### 4.2.3 Module Power Supply Specification

In order to avoid exceeding the host system power capacity, upon hot-plug, power cycle or reset, all QSFP-DD modules shall power up in Low Power Mode if InitMode is asserted. If InitMode is not asserted the module will proceed to High Power Mode without host intervention. Figure 7 shows waveforms for maximum instantaneous, sustained and steady state currents for Low Power and High Power modes. Specification values for maximum instantaneous, sustained and steady state currents at each power class are given in Table 4.

#### 4.2.4 Host Board Power Supply Noise Output

The host shall generate an effective weighted integrated spectrum RMS noise less than the value in Table 4 when tested by the methods of SFF-8431, section D.17.1.

#### 4.2.5 Module Power Supply Noise Output

The QSFP-DD module shall generate less than the value in Table 4 when tested by the methods of SFF-8431, section D.17.2. Note: The series resister specified in D.17 Figure 56 may need to be reduced for high power modules.

#### 4.2.6 Module Power Supply Noise Tolerance

The QSFP-DD module shall meet all requirements and remain fully operational in the presence of a sinusoidal tolerance signal of amplitude given by Table 4, swept from 10 Hz to 10 MHz according to the methods of SFF-8431, section D.17.3. This emulates the worst case noise output of the host.

| Parameter                                                                               | Symbol                            | Min        | Nom     | Max           | Unit      |

|-----------------------------------------------------------------------------------------|-----------------------------------|------------|---------|---------------|-----------|

| Power supply voltages VccTx, VccTx1,                                                    |                                   | 3.135      | 3.3     | 3.465         | V         |

| VccRx, VccRx1, Vcc1 & Vcc2 including                                                    |                                   |            |         |               |           |

| ripple, droop and noise below 100kHz <sup>1</sup>                                       |                                   |            |         |               |           |

| Host RMS noise output 10 Hz-10 MHz                                                      |                                   |            |         | 25            | mV        |

| Module RMS noise output 10 Hz - 10 MHz                                                  |                                   |            |         | 15            | mV        |

| Module power supply noise tolerance 10 Hz                                               | $PSNR_{mod}$                      |            |         | 66            | mV        |

| - 10 MHz (peak-to-peak)                                                                 |                                   |            |         |               |           |

| Module inrush - instantaneous peak                                                      | T_ip                              |            |         | 50            | μs        |

| duration                                                                                |                                   |            |         | 500           |           |

| Module inrush - initialization time                                                     | T_init<br>Power Mode <sup>2</sup> |            |         | 500           | ms        |

| Power Consumption                                                                       | P_lp                              |            |         | 1.0           | W         |

| ***************************************                                                 |                                   | _          | _       | 400           |           |

| Instantaneous peak current at hot plug<br>Sustained peak current at hot plug            | Icc_ip_lp                         | _          | _       | 330           | mA<br>mA  |

| Steady state current                                                                    | Icc_sp_lp<br>Icc_lp               | _          | _       | 288           | mA        |

|                                                                                         | lass 1 module                     | -          | -       | 200           | IIIA      |

|                                                                                         | P_1                               |            | 1       | 1.0           | W         |

| Power Consumption                                                                       |                                   | -          | _       |               |           |

| Instantaneous peak current                                                              | Icc_ip_1<br>Icc_sp_1              | -          | -       | 400<br>330    | mA<br>mA  |

| Sustained peak current                                                                  | Icc 1                             | -          | -       |               | mA<br>mA  |

| Steady state current                                                                    | lass 2 module                     | -          | -       | 288           | mA        |

| Power Consumption                                                                       | P_2                               |            |         | 3.5           | W         |

| -                                                                                       | Icc_ip_2                          | _          | _       | 1400          |           |

| Instantaneous peak current<br>Sustained peak current                                    |                                   | -          | -       | 1400          | mA<br>mA  |

|                                                                                         | Icc_sp_2<br>Icc 2                 | -          | _       | 1010          |           |

| Steady state current                                                                    | lass 3 module                     | -          | -       | 1010          | mA        |

| Power Consumption                                                                       | P_3                               |            |         | 7             | W         |

|                                                                                         |                                   | -          | -       | 2800          |           |

| Instantaneous peak current<br>Sustained peak current                                    | Icc_ip_3                          | _          | -       | 2310          | mA<br>mA  |

| Steady state current                                                                    | Icc_sp_3<br>Icc 3                 | -          | -       | 2020          | mA        |

|                                                                                         | lass 4 module                     | -          | _       | 2020          | IIIA      |

| Power Consumption                                                                       |                                   |            | 1       | 8             | W         |

|                                                                                         | P_4<br>Icc_ip_4                   |            |         | 3200          |           |

| Instantaneous peak current<br>Sustained peak current                                    | ICC_1p_4<br>ICC_sp_4              | -          | -       | 2640          | mA<br>mA  |

| Steady state current                                                                    | Icc 4                             | -          | -       | 2308          | mA        |

| -                                                                                       | lass 5 module                     | -          | _       | 2300          | IIIA      |

|                                                                                         |                                   |            | 1       | 10            | W         |

| Power Consumption<br>Instantaneous peak current                                         | P_5<br>Icc_ip_5                   |            | _       | 4000          | mA        |

| Sustained peak current                                                                  |                                   | _          | -       | 3300          |           |

| 1                                                                                       | Icc_sp_5                          | -          | -       | 2886          | mA<br>mA  |

| Steady state current                                                                    | Icc_5                             | -          | -       | 2000          | IIIA      |

| Power Consumption                                                                       | P_6                               | 1          |         | 12            | W         |

|                                                                                         |                                   |            |         | 4800          |           |

| Instantaneous peak current                                                              | Icc_ip_6                          | -          | -       | 3960          | mA<br>mA  |

| Sustained peak current                                                                  | Icc_sp_6                          | -          | -       |               | mA<br>m D |

| Steady state current                                                                    | ICC_6                             | -          | -       | 3463          | mA        |

|                                                                                         | lass 7 module                     | 1          |         | 1.4           | 7.7       |

| Power Consumption                                                                       | P_7                               | _          | _       | 14<br>5600    | W         |

| Instantaneous peak current                                                              | Icc_ip_7                          |            |         |               | mA        |

| Sustained peak current                                                                  | Icc_sp_7                          | -          | -       | 4620          | mA<br>mA  |

| Steady state current                                                                    | Icc_7                             | -          | -       | 4040          | mA        |

|                                                                                         | lass 8 module                     | 1          |         | . 1 /         | T.7       |

| Power Consumption                                                                       | P_8 <sup>3</sup>                  |            | +       | >14           | W         |

| Instantaneous peak current                                                              | Icc_ip_8                          | -          | -       | P_8/2.5       | A         |

| Sustained peak current                                                                  | Icc_sp_8                          | -          | -       | P_8/3.03      | A         |

| Steady state current                                                                    | Icc_8                             | -          | -       | P_8/3.465     | A         |

| Note 1: Measured at VccTx, VccTx1, VccRx,<br>Note 2: Host designers are responsible for |                                   |            | er Mode | e QSFP legacy |           |

| modules as appropriate in their system.<br>Note 3: User must read register 229 for ma   | aximum power co                   | onsumptior | ı       |               |           |

### 4.3 ESD

Where ESD performance is not otherwise specified, e.g. in the InfiniBand specification, the QSFP-DD module shall meet ESD requirements given in EN61000-4-2, criterion B test specification when installed in a properly grounded cage and chassis. The units are subjected to 15kV air discharges during operation and 8kV direct contact discharges to the case. All the QSFP-DD module and host pins including high speed signal pins shall withstand 1000 V electrostatic discharge based on Human Body Model per ANSI/ESDA/JEDEC JS-001.

# 5 Mechanical and Board Definition

# 5.1 Introduction

The cages and modules defined in this section are illustrated in Figure 8 (2x1 stacked cage), Figure 9 (surface mount cage) and Figure 10 (pluggable module). All Pluggable modules and direct attach cable plugs must mate to the connectors and cages defined in this specification. Heat sink/clip thermal designs are application specific and not specifically defined by this specification.

Figure 8: 2x1 stacked cage and module

Figure 9: Press fit cage for surface mount (SMT) connector

Figure 10: Pluggable module

# 5.2 Datums, Dimensions and Component Alignment